半導(dǎo)體行業(yè)專題報(bào)告:封測產(chǎn)業(yè)鏈機(jī)遇將至

2023-10-17 17:03

(報(bào)告出品方:國金證券)

一、先進(jìn)封裝:后摩爾時(shí)代提升系統(tǒng)性能的關(guān)鍵路徑

1.1、摩爾定律放緩,先進(jìn)封裝接力先進(jìn)制程助力持續(xù)發(fā)展

摩爾定律發(fā)展放緩,集成電路產(chǎn)業(yè)尋求新的發(fā)展路線。根據(jù)摩爾定律,集成電路上可以容 納的晶體管數(shù)目在大約每經(jīng)過 18 個(gè)月到 24 個(gè)月便會(huì)增加一倍,處理器性能大概每兩年 翻一倍,同時(shí)價(jià)格下降為之前的一半。集成電路產(chǎn)業(yè)主要沿著兩條技術(shù)路線發(fā)展:一是延 續(xù)摩爾定律,芯片向小型化發(fā)展。通過縮小 CMOS 器件的晶體管尺寸來增加芯片的晶體管 數(shù)量,進(jìn)而提升芯片性能。二是超越摩爾定律,采取先進(jìn)封裝技術(shù)將模擬、光電、傳感等 集成在一個(gè)系統(tǒng)內(nèi),實(shí)現(xiàn)系統(tǒng)的性能提升和功能融合。目前,先進(jìn)制程工藝逐漸逼近物理 極限,越來越多的廠商開始將研發(fā)方向由先前的“如何把芯片變得更小”轉(zhuǎn)變?yōu)?ldquo;如何把 芯片封得更小”,先進(jìn)封裝逐漸成為行業(yè)發(fā)展重點(diǎn)。

先進(jìn)封裝正進(jìn)入快速發(fā)展的階段。集成電路封裝行業(yè)大致劃分為五個(gè)發(fā)展階段。第一階段 為通孔插裝時(shí)代,以 DIP、SIP 技術(shù)為代表。第二階段是表面貼裝時(shí)代,該階段以 LCC、 SOP 為代表,用引線替代第一階段的引腳并貼裝在 PCB 板上,相對(duì)而言封裝體積減少、封 裝密度有所提高。第三階段是面積陣列時(shí)代,開始出現(xiàn) BGA、CSP、FC 等先進(jìn)封裝技術(shù), 這一階段是目前全球封測廠商所處的主流技術(shù)階段,此階段引線已被取消,在封裝體積大 幅縮減的同時(shí)提升了系統(tǒng)性能。封裝技術(shù)的第四階段,工藝從單芯片變?yōu)槎嘈酒姆庋b 元件演化為封裝系統(tǒng),MCM、SiP、Bumping 等技術(shù)發(fā)展迅速。此后,微機(jī)電機(jī)械系統(tǒng)封裝 (MEMS)、硅通孔(TSV)、扇出型封裝(Fan-Out)等立體結(jié)構(gòu)型封裝技術(shù)相繼出現(xiàn),帶動(dòng) 封裝產(chǎn)業(yè)鏈進(jìn)入復(fù)雜集成時(shí)代。

對(duì)比傳統(tǒng)封裝技術(shù),先進(jìn)封裝 I/O 數(shù)量多、體積小且高度集成化。在傳統(tǒng)的封裝技術(shù)中, 晶圓被切割后通過引線鍵合的方式實(shí)現(xiàn)互聯(lián),起到保護(hù)芯片的作用。而外部封裝則是通過 導(dǎo)線架或?qū)Ь€載板與 PCB 基板進(jìn)行連接,這種封裝形式結(jié)構(gòu)簡單、成本低廉。但隨著集成 電路產(chǎn)業(yè)的高速發(fā)展,市場對(duì)于電子設(shè)備的小型化、系統(tǒng)化和信息傳遞速度等的要求不斷 提高,先進(jìn)封裝逐漸成為行業(yè)主流技術(shù)。先進(jìn)封裝運(yùn)用凸塊等工藝,采用倒裝等鍵合方式 替代傳統(tǒng)的引線鍵合,在縮短互聯(lián)距離的同時(shí)提高 I/O 密度,具有更高的存儲(chǔ)帶寬和更好 的散熱效率。同時(shí)封裝對(duì)象由單裸片發(fā)展為多裸片,芯片組合由單類型、平面排布向多功 能、立體堆疊演變,顯著提高了封裝空間利用率和芯片系統(tǒng)性能。

集成電路發(fā)展受阻,先進(jìn)封裝或?yàn)槠茐κ走x。當(dāng)前集成電路的發(fā)展面臨著“存儲(chǔ)墻、面積 墻、功耗墻以及功能墻”四座高墻的制約。 存儲(chǔ)墻:全球計(jì)算算力約每兩年增長 3.1 倍,而存儲(chǔ)帶寬每兩年增長 1.4 倍,存儲(chǔ)器 帶寬增長速度明顯落后處理器。為了突破“存儲(chǔ)墻”,業(yè)界提出了近存計(jì)算方案,通 過先進(jìn)封裝為基礎(chǔ)的超短互連技術(shù)實(shí)現(xiàn)存儲(chǔ)器和處理器間的近距離數(shù)據(jù)搬運(yùn),其算 力和精度更高。 面積墻:目前光刻機(jī)所能支持的最大曝光區(qū)域面積是 26mm*33mm,增加光罩面積來提 升晶體管集成數(shù)量的話方案成本極高,而采用先進(jìn)封裝技術(shù)集成多顆芯片則是目前 主流的低成本破局方案。 功耗墻:隨著芯片算力需求的提升,GPU/CPU 芯片熱設(shè)計(jì)功耗逐年增大,或?qū)⑼黄魄?瓦級(jí),需更為先進(jìn)的冷卻技術(shù)以支持散熱需要。功能墻:在單個(gè)芯片襯底上可實(shí)現(xiàn)的功能有限,通過先進(jìn)封裝的多芯片異質(zhì)集成技術(shù) 將計(jì)算、存儲(chǔ)、傳感等功能元件集成起來,可以突破單襯底的功能限制。

1.2、先進(jìn)封裝發(fā)展迅速,各路線百花齊放

集成電路封測市場規(guī)模逐年增長。根據(jù) Yole 及集微咨詢的統(tǒng)計(jì)數(shù)據(jù),2022 年全球封測市 場規(guī)模為 815.0 億美元,同比增長 4.9%,預(yù)計(jì)到 2026 年市場規(guī)模有望達(dá) 961.0 億美元, 2022 年-2026 年 CAGR 為 4.2%。中國大陸作為封測產(chǎn)業(yè)的三大市場之一,市場規(guī)模呈增長 趨勢。據(jù)中國半導(dǎo)體行業(yè)協(xié)會(huì)以及集微咨詢數(shù)據(jù),2022 年中國大陸封測市場規(guī)模為 2995.0 億元,預(yù)計(jì)到 2026 年市場規(guī)模有望達(dá) 3248.4 億元。

先進(jìn)封裝市場規(guī)模及占比持續(xù)提升,中國大陸先進(jìn)封裝占比有望不斷提高。據(jù) Yole 及集 微咨詢數(shù)據(jù),2022 年全球先進(jìn)封裝市場規(guī)模為 378.0 億美元,到 2026 年全球先進(jìn)封裝市 場規(guī)模達(dá) 482.0 億美元,2022 年-2026 年全球先進(jìn)封裝市場規(guī)模 CAGR 為 6.3%,先進(jìn)封裝 占比有望突破 50%。中國大陸的先進(jìn)封裝市場規(guī)模有望快速成長,據(jù)中國半導(dǎo)體行業(yè)協(xié)會(huì) 統(tǒng)計(jì)及集微咨詢數(shù)據(jù),2020年中國大陸先進(jìn)封裝市場規(guī)模為903億元,市場占比僅為36%, 預(yù)計(jì) 2023 年中國先進(jìn)封裝市場規(guī)模預(yù)計(jì)達(dá) 1330 億元,2020-2023 年 4 年的復(fù)合增長率約 為 13.8%。但是,目前國內(nèi)先進(jìn)封裝市場占比僅為 39.0%,與全球先進(jìn)封裝市場占比(48.8%) 相比仍有較大差距,有較大提升潛力。

先進(jìn)封裝市場以倒裝工藝為主,未來 3D 先進(jìn)封裝技術(shù)占比將進(jìn)一步提升。根據(jù) Yole 及集 微咨詢數(shù)據(jù),倒裝(FC)封裝技術(shù)是目前市場份額最大的板塊,2022 年全球倒裝封裝技術(shù) 市場規(guī)模為 290.9 億美元,占比達(dá) 76.7%,到 2026 年其市場規(guī)模有望增加至 340.32 億美 元。其他高階的封裝形式(如 Fan-Out、3D Stacked)占比將有所提升,其中 3D Stacked 技術(shù)市場規(guī)模增長速度最快,2019 年-2026 年期間的復(fù)合年增長率為 22.7%,預(yù)計(jì) 2026 年 市場份額將達(dá)到 15.3%。

先進(jìn)封裝的四大要素推動(dòng)著封裝技術(shù)向連接密集化、堆疊多樣化和功能系統(tǒng)化方向發(fā)展。

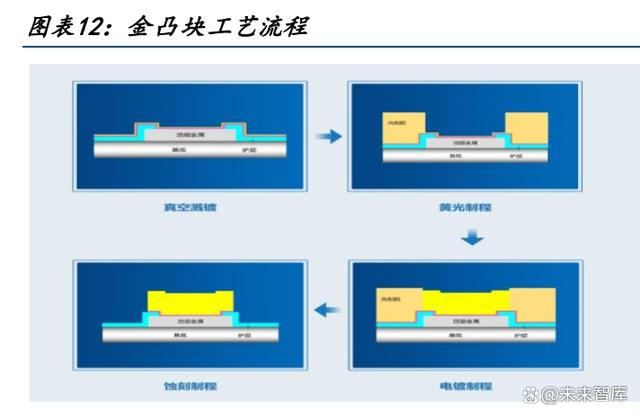

1)凸塊(Bump)技術(shù)運(yùn)用于倒裝封裝中,是早期先進(jìn)封裝區(qū)別于傳統(tǒng)封裝的一個(gè)顯 著特征。該工藝通過在晶圓或芯片表面焊接球狀或柱狀金屬凸點(diǎn)來實(shí)現(xiàn)界面間的電 氣互聯(lián)和應(yīng)力緩沖。隨著技術(shù)進(jìn)步,凸塊尺寸越來越小,發(fā)展出不需要凸塊的混合鍵 合(Hybrid Bonding)互聯(lián)方式,連接密度大幅提升。 根據(jù)凸塊材料的不同,凸塊工藝可分為四類: 1.金凸塊工藝:(1)濺鍍,用高速離子對(duì)金屬進(jìn)行轟擊,使其表面沉積一層金屬層; (2)上膠,在晶圓表面涂一層光刻膠,再通過光模板進(jìn)行曝光,浸入顯影液后膠部 分溶解,從而在光刻膠上對(duì)凸塊位置開窗;(3)電鍍,將晶圓浸入電鍍液,在電流差 的作用下金屬離子移動(dòng)到開窗位置形成凸塊;(4)去膠、蝕刻,去除多余的光刻膠并 通過蝕刻去除凸塊周圍的金屬層。 2.銅柱凸塊工藝:(1)再鈍化,在晶圓上的凸塊位置附近涂抹聚合物或金屬形成鈍化 層,以提供芯片保護(hù)及結(jié)構(gòu)支撐作用;(2)濺鍍;(3)上膠;(4)電鍍;(5)去膠、 蝕刻;(6)回流,運(yùn)用助焊劑對(duì)焊料進(jìn)行多次回流,形成光滑的截球形凸塊。

3.銅鎳金凸塊工藝:工藝流程與金凸塊工藝流程相似,區(qū)別在于(1)銅鎳金凸塊的 表面面積更大,改變了芯片的部分線路結(jié)構(gòu),鍵合靈活性更高;(2)凸塊中銅占比較 高,大幅降低成本和導(dǎo)通電阻。

4.錫凸塊工藝:工藝流程與銅柱凸塊工藝流程相似,區(qū)別在于(1)球體體積更大, 是銅柱凸塊尺寸的 3-5 倍,可焊性更強(qiáng)(也可以采用電鍍工藝回流形成大直徑錫球); (2)分為電鍍焊錫和植球焊錫兩類,前者尺寸更小,可用于小尺寸封裝,后者使用 更大的焊錫球來形成接點(diǎn),可以增加元件與基板底材之間的距離,緩沖基板與元件間 因熱膨脹差異而產(chǎn)生的應(yīng)力,增加元件的可靠性。

2)重布線層(RDL)技術(shù)是用于水平方向電氣延伸和互聯(lián)的技術(shù)。由于 I/0 觸點(diǎn)通常 分布芯片四周,如果直接進(jìn)行倒裝封裝會(huì)因?yàn)橐€過少或過密影響連接效果,而 RDL 通過對(duì)芯片上的觸點(diǎn)進(jìn)行重新布局和導(dǎo)電,改變芯片管腳的分布或?qū)⒐苣_引出到外 圍寬松的區(qū)域,從而降低封裝難度并增加 I/O 引腳數(shù)量。 RDL 工藝需要曝光、PVD 等設(shè)備,具體工藝流程如下:(1)再鈍化形成絕緣層并開口; (2)利用旋涂膜技術(shù)涂覆烘烤后形成種子層;(3)上光刻膠,曝光顯影后形成線路 圖再電鍍銅墊;(4)去膠、刻蝕;(5)第一層布線完成后重復(fù)步驟,開始形成第二層。

3)晶圓(wafer)技術(shù)是先進(jìn)封裝在封裝對(duì)象層面實(shí)現(xiàn)突破的工藝基礎(chǔ)。在傳統(tǒng)封裝 中,裸片先進(jìn)行切割分片再各自封裝,而晶圓級(jí)封裝(WLP)則是在晶圓的基礎(chǔ)上直 接封裝再進(jìn)行切割分片,封裝面積與裸片一致,可以提高封裝效率并降低封裝成本。

4)硅通孔(TSV)技術(shù)是在垂直方向上進(jìn)行電氣延伸和互聯(lián)的技術(shù),也是實(shí)現(xiàn)三維立 體堆疊和系統(tǒng)集成的基礎(chǔ)。該技術(shù)通過在硅中介層或芯片中插入垂直的金屬填通孔, 短距離連接上下層芯片,可以實(shí)現(xiàn)高帶寬低延時(shí)的信息傳遞,被大量應(yīng)用于系統(tǒng)級(jí)封 裝(如 2.5D/3D 封裝)。 TSV 工藝需要 DRIE、CVD、PVD、CMP 等設(shè)備,具體工藝流程如下:(1)通孔刻蝕,運(yùn) 用激光刻蝕、濕法刻蝕或深反應(yīng)離子刻蝕技術(shù)在硅片上打孔;(2)在硅孔內(nèi)形成絕緣 層,防止通孔間漏電或串?dāng)_;(3)運(yùn)用物理氣相沉積等方法形成阻擋層和種子層;(4) 運(yùn)用電鍍工藝在通孔內(nèi)填充銅、鎢、多晶硅等金屬材料;(5)運(yùn)用 CMP 工藝對(duì)晶圓片 進(jìn)行拋光減薄;(6)使用粘合劑、金屬或氧化物實(shí)現(xiàn)多層硅芯片的堆疊和鍵合。

倒裝封裝:是直接在芯片 I/O 焊盤上或 RDL 重布線層上沉積凸塊,然后將芯片電氣面朝 下,倒扣在封裝襯底上實(shí)現(xiàn)電氣互聯(lián)的封裝技術(shù)。與傳統(tǒng)封裝引線鍵合(Wire Bonding) 方式相比,倒裝技術(shù)大幅縮短了互聯(lián)距離,電阻電感更小,芯片電性能和散熱性更好。同 時(shí)緊湊的結(jié)構(gòu)排布使得封裝具有更小的尺寸和更強(qiáng)的抗沖擊性,對(duì)于移動(dòng)設(shè)備和工業(yè)應(yīng)用 等領(lǐng)域具有重要意義。

晶圓級(jí)封裝:是對(duì)整片晶圓進(jìn)行封裝測試后再切割得到單個(gè)成品芯片的技術(shù)。對(duì)比傳統(tǒng)封 裝先切割晶圓再逐個(gè)封裝的流程,晶圓級(jí)封裝技術(shù)直接在晶圓上完成封測程序后進(jìn)行批量 化切割,封裝與芯片制造融為一體,大幅縮減生產(chǎn)成本。同時(shí)該類封裝不需要引線框架、 基板等介質(zhì),可以最大程度地提高封裝效率,封裝后的芯片尺寸與裸片一致。 扇出型封裝:晶圓級(jí)封裝分為扇入型封裝(Fan-in)和扇出型封裝兩種,扇入型封裝利用 RDL 層將電信號(hào)向內(nèi)擴(kuò)展至芯片中心,封裝尺寸基本等于芯片尺寸,可容納的 I/O 數(shù)量較 少,多用于小型便攜產(chǎn)品。但隨著技術(shù)進(jìn)步,對(duì)于芯片 I/O 數(shù)量的要求不斷提升,扇出型 封裝應(yīng)運(yùn)而生。扇出型封裝是在芯片的范圍之外利用 RDL 重布層,將電信號(hào)向外擴(kuò)展至芯 片外的區(qū)域(扇出區(qū)),因此可以連接更多引腳。相比于扇入型,扇出型封裝具有更好的 擴(kuò)展能力、電氣性能和熱性能,多用于基帶處理器、射頻收發(fā)器、5G、醫(yī)療器件處理器等 低耗高頻高速的設(shè)備中。

2.5D/3D 封裝:2.5D 封裝和 3D 封裝是多芯片立體堆疊的封裝技術(shù)。兩者的主要區(qū)別在于 電互聯(lián)的實(shí)現(xiàn)方式,2.5D 封裝是在中介層(interposer)上打孔布線來展開水平互聯(lián),3D 封裝則是直接在芯片上打孔布線實(shí)現(xiàn)垂直方向的上下層連接。從制造結(jié)構(gòu)來看,2.5D 封 裝的芯片倒扣在中介層(interposer)之上,通過一系列的微凸塊和硅通孔實(shí)現(xiàn)不同功能 裸片和基底之間的連接,具有高密度、低功耗和低延遲的特性。而 3D 封裝不需要中介層, 芯片通過 TSV 多層垂直堆疊直接實(shí)現(xiàn)高密度互連,提高了 IC 的性能;同時(shí)因?yàn)樗试S更 加緊湊的布線設(shè)計(jì),減少了信號(hào)傳輸?shù)淖枇Γ档土?IC 的功耗。 系統(tǒng)級(jí)封裝(System in Package,SiP):是將多種功能芯片(包括處理器、存儲(chǔ)器等)集 成在一個(gè)封裝內(nèi),從而實(shí)現(xiàn)完整功能的封裝方式。目前電路集成化的實(shí)現(xiàn)主要有系統(tǒng)級(jí)封 裝和系統(tǒng)級(jí)芯片(System on a Chip,SoC)兩條技術(shù)路徑。SoC 是將具有不同功能的元 器件整合在單個(gè)芯片中的技術(shù),一顆芯片即為一個(gè)高度集成系統(tǒng),其信息傳遞效率更高、 體積更小,缺點(diǎn)在于其設(shè)計(jì)開發(fā)的周期更長,技術(shù)性要求更高,開發(fā)成本更高,因此多應(yīng) 用于對(duì)運(yùn)算功能要求高的高單價(jià) GPU、HPC 等。而系統(tǒng)級(jí)封裝是將單顆功能復(fù)雜的 SoC 集 成芯片剝離成多個(gè)具有特定功能的芯片(Chiplet),再采用 TSV、interposer 等工藝形成多功能異質(zhì)異構(gòu)的封裝,其開發(fā)周期更短、良率更高、成本更低,是目前平衡功能與經(jīng)濟(jì) 效益的最優(yōu)選擇。

1.3、Chiplet 助力 AI 算力芯片持續(xù)發(fā)展

Chiplet 提升大芯片制造良率,降低生產(chǎn)制造成本

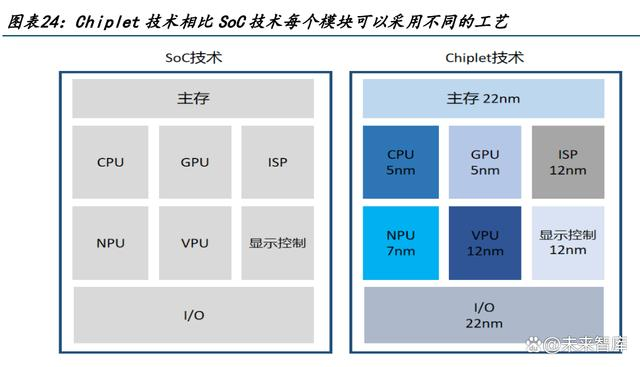

經(jīng) Chiplet 架構(gòu)設(shè)計(jì)后,不同的 die(芯片裸片)之間采用先進(jìn)封裝互聯(lián)。Chiplet 指小 型模塊化芯片,通過 die-to-die 內(nèi)部互聯(lián)技術(shù)將多個(gè)模塊芯片與底層基礎(chǔ)芯片封裝在一 起形成一個(gè)整體的內(nèi)部芯片。與 SoC 不同,Chiplet 將不同模塊從設(shè)計(jì)時(shí)就按照不同計(jì)算 或者功能單元進(jìn)行分解,制作成不同 die 后使用先進(jìn)封裝技術(shù)互聯(lián)封裝,不同模塊制造工 藝可以不同。

Chiplet 相比傳統(tǒng) SoC 芯片優(yōu)勢明顯。Chiplet 能利用最合理的工藝滿足數(shù)字、射頻、模 擬、I/O 等不同模塊的技術(shù)要求,把大規(guī)模的 SoC 按照功能分解為模塊化的芯粒,在保持 較高性能的同時(shí),大幅度降低了設(shè)計(jì)復(fù)雜程度,有效提高了芯片良率、集成度,降低芯片 的設(shè)計(jì)和制造成本,加速了芯片迭代速度。

HBM 的應(yīng)用解決了內(nèi)存速率瓶頸

HBM(High Bandwidth Memory)即高帶寬存儲(chǔ)器,其通過使用先進(jìn)的封裝方法(如 TSV 硅 通孔技術(shù))垂直堆疊多個(gè) DRAM。在高性能計(jì)算應(yīng)用對(duì)內(nèi)存速率提出了更高的要求的背景 下,使用先進(jìn)封裝工藝的 HBM 很好的解決了傳統(tǒng) DRAM 的內(nèi)存速率瓶頸的問題。HBM 內(nèi)部 的 DRAM 堆疊屬于 3D 封裝,而 HBM 與 AI 芯片的其他部分合封于 Interposer 上屬于 2.5D 封裝。

堆疊子模塊,提升計(jì)算性能

Chiplet 支持多顆計(jì)算 die 合封于同一芯片,通過堆疊實(shí)現(xiàn)處理能力的提升。AMD 于 2023 年 6 月發(fā)布了 MI300 產(chǎn)品,該芯片擁有 13 個(gè)小芯片,共包括 9 個(gè) 5nm 的計(jì)算核心(6 個(gè) GCD+3 個(gè) CCD),4 個(gè) 6nm 的 I/O die 兼 Infinity Cache(同時(shí)起到中介層的作用,位于計(jì) 算核心和 interposer 之間),同時(shí)還搭載了累計(jì) 8 顆共計(jì) 128GB 的 HBM3 芯片。

助力國產(chǎn)半導(dǎo)體廠商突破海外制裁

Chiplet 技術(shù)發(fā)展?jié)摿Υ螅型a(chǎn)半導(dǎo)體廠商突破海外科技領(lǐng)域制裁。2020 年美國 將中芯國際列入“實(shí)體清單”,限制 14nm 及以下制程的擴(kuò)產(chǎn),導(dǎo)致國產(chǎn) 14nm 制程處于存 量市場無法擴(kuò)張。Chiplet 技術(shù)可部分規(guī)避海外限制,向下超越封鎖:1)Chiplet“化整 為零”,將單顆芯片裸片面積縮小,使壞點(diǎn)出現(xiàn)時(shí)對(duì)整體晶圓的影響縮小,即良率提高, 因此在國內(nèi) 14nm 產(chǎn)能為存量的局面下提升了實(shí)際芯片產(chǎn)出。2)Chiplet 可僅對(duì)核心模塊 如 CPU、GPU 采用先進(jìn)制程,對(duì)其他模塊采用成熟制程,有效降低對(duì)先進(jìn)制程的依賴,減 少了 14nm 晶圓的用量。3)Chiplet 可通過將兩顆 14nm 芯片堆疊互聯(lián),單位面積晶體管 數(shù)量翻倍,實(shí)現(xiàn)超越 14nm 芯片的性能。因此 Chiplet 技術(shù)成為中國半導(dǎo)體行業(yè)實(shí)現(xiàn)彎道 超車的逆境突破口之一。

二、行業(yè)周期:觸底持續(xù)進(jìn)行,底部反轉(zhuǎn)或?qū)⒌絹?/font>

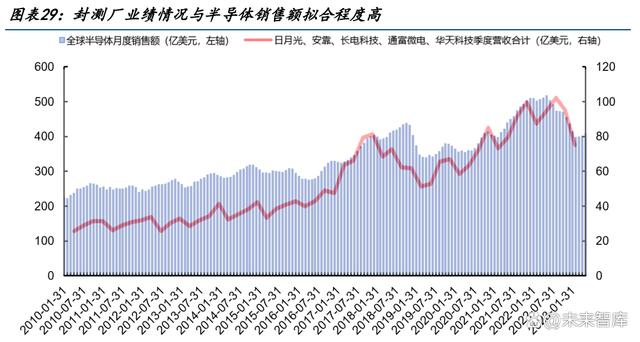

封測廠營收與半導(dǎo)體銷售額呈高度擬合關(guān)系。從產(chǎn)業(yè)鏈位置來看,封測屬半導(dǎo)體產(chǎn)業(yè)鏈中 位置相對(duì)靠后的環(huán)節(jié),封測廠生產(chǎn)的產(chǎn)品將成為最終產(chǎn)品形態(tài)并進(jìn)入設(shè)計(jì)廠商庫存。因此, 在庫存水位較高的情況下,受 IC 設(shè)計(jì)廠商砍單影響,封測廠商表現(xiàn)會(huì)相對(duì)較弱,業(yè)績出 現(xiàn)明顯下滑;但若當(dāng)下游需求好轉(zhuǎn)情況下,IC 設(shè)計(jì)廠商會(huì)優(yōu)先向封測廠商加單,加工處理 之前積累的未封裝晶圓,進(jìn)而推動(dòng)整體產(chǎn)業(yè)鏈從底部實(shí)現(xiàn)反轉(zhuǎn)。從規(guī)模上看,封測廠營收 趨勢與全球半導(dǎo)體銷售額基本一致。

下游出貨量持續(xù)低迷是半導(dǎo)體景氣度下滑的重要因素。按下游占比來看,移動(dòng)通信和計(jì)算 機(jī)是半導(dǎo)體最大的兩個(gè)下游應(yīng)用終端產(chǎn)品,移動(dòng)通信約占 30%,計(jì)算機(jī)終端市場約占 26%, 汽車、工業(yè)和其他消費(fèi)類電子占據(jù)了其余部分。而手機(jī)和電腦的出貨量持續(xù)低迷,處在持 續(xù)探底的過程中,根據(jù) Gartner2023 年 1 月發(fā)布的預(yù)測數(shù)據(jù),2023 年全球 PC、智能手機(jī) 出貨量分別為 2.68 億臺(tái)、13.4 億臺(tái),較 2022 年分別-6.5%、-4.0%。

國內(nèi)芯片設(shè)計(jì)公司整體庫存維持在較高水位,部分公司庫存拐點(diǎn)已現(xiàn)。受供需雙重作用, 國內(nèi)芯片設(shè)計(jì)上市公司在 2021 年-2022Q3 庫存水平持續(xù)攀升。從供給端來看,自 2020 年 受特殊因素影響,全球出現(xiàn)芯片短缺,各大半導(dǎo)體制造企業(yè)積極擴(kuò)產(chǎn)。伴隨新產(chǎn)能陸續(xù)釋 放,全球半導(dǎo)體產(chǎn)能出現(xiàn)供給過剩。從需求端來看,受外部環(huán)境及美聯(lián)儲(chǔ)加息等影響,下 游消費(fèi)需求持續(xù)疲軟,半導(dǎo)體銷售額持續(xù)下降。在供需雙重作用下,設(shè)計(jì)廠商進(jìn)入被動(dòng)補(bǔ) 庫存階段。 但是,我們判斷行業(yè)拐點(diǎn)或?qū)⒊霈F(xiàn),部分設(shè)計(jì)廠商目前已從“被動(dòng)補(bǔ)庫存”階段陸續(xù)進(jìn)入 “主動(dòng)去庫存階段”。22Q4-23Q1 已經(jīng)有部分芯片設(shè)計(jì)廠商庫存水位下降,大多數(shù)芯片設(shè) 計(jì)公司庫存呈企穩(wěn)態(tài)勢。展望未來,芯片設(shè)計(jì)公司庫存壓力將有望隨下游需求邊際向好而 繼續(xù)改善。

封測行業(yè)重資產(chǎn)屬性強(qiáng),利潤受稼動(dòng)率影響較大。封測行業(yè)呈現(xiàn)重資產(chǎn)屬性的特質(zhì),固定 資產(chǎn)的比重相對(duì)較大。稼動(dòng)率受下游廠商庫存水位偏高的影響,相對(duì)處于低位。固定資產(chǎn) 的折舊占成本比重較大,在行業(yè)下行周期內(nèi)會(huì)對(duì)利潤造成較大影響。但展望未來,一旦下 游需求好轉(zhuǎn),渠道庫存下降,利潤增長的彈性較大。

筑底已基本完成,封測大廠業(yè)績有望逐季改善。從下游需求來看,至暗時(shí)刻已過,部分設(shè) 計(jì)廠商庫存水位下降,已進(jìn)入主動(dòng)去庫存階段。下半年,部分海外廠商將備貨新產(chǎn)品,對(duì) 于封測端的需求有望提升。臺(tái)灣力成在 7 月 25 日法說會(huì)表示,維持今年業(yè)績逐季改善的 看法,二季度業(yè)績優(yōu)于一季度,預(yù)計(jì)第三季營收也將優(yōu)于第二季度。此外,受益于 AI 浪 潮的拉動(dòng),先進(jìn)封裝產(chǎn)能吃緊。從產(chǎn)業(yè)趨勢來看,有先進(jìn)封裝能力及汽車電子封測業(yè)務(wù)的 公司,將在本輪復(fù)蘇中更為受益。

三、海外大廠技術(shù)布局

3.1、臺(tái)積電

臺(tái)積電作為產(chǎn)業(yè)龍頭,早在 2008 年底就成立了專門的導(dǎo)線與封裝技術(shù)整合部門來研發(fā)封 裝技術(shù),經(jīng)過十余年的技術(shù)研發(fā)積累了多款先進(jìn)封裝技術(shù),并于 2020 年宣布推出 3D Fabric™品牌,進(jìn)一步整合公司制程工藝和封裝技術(shù)。3D Fabric™包括前段系統(tǒng)整合芯片 技術(shù)(SoIC)和后段基板上芯片封裝技術(shù)(CoWoS)和整合型扇出封裝技術(shù)(InFO)。

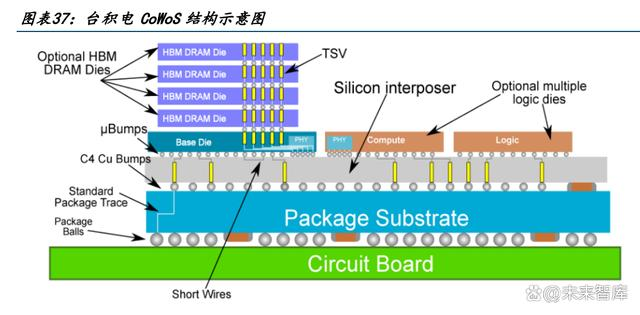

1)CoWoS(Chip on Wafer on Substrate)是臺(tái)積電 2011 年推出的首個(gè) 2.5D 先進(jìn)封裝技 術(shù),包括 CoWoS-S、CoWoS-R 和 CoWoS-L 三類。 CoWoS-S 包括 CoW 和 oS 兩部分,芯片間通過 CoW 工藝與硅晶圓相連,再通過凸塊將 CoW 芯片與基板相連。該技術(shù)用微凸塊和硅穿孔工藝代替?zhèn)鹘y(tǒng)引線鍵合,將不同功能 的芯片堆疊在同一個(gè)硅中介層上實(shí)現(xiàn)互聯(lián),具有縮小封裝尺寸、降低功耗、提升系統(tǒng) 性能的優(yōu)點(diǎn)。 CoWoS-R 是扇出型晶圓級(jí)封裝,該技術(shù)利用 RDL 內(nèi)插件實(shí)現(xiàn)芯片間的互連(常用于 HBM 和 SoC 的異構(gòu)集成),RDL 重布線層由聚合物和銅線組成,具有較高的機(jī)械靈活性。這 種靈活性提高了 C4 連接的完整性,可以擴(kuò)大封裝尺寸以滿足更復(fù)雜的功能需求。 CoWoS-L 是扇出型晶圓級(jí)封裝,它結(jié)合了 CoWoS-S 和 InFO 技術(shù)的優(yōu)點(diǎn),通過使用帶 有 LSI(局部硅互連)芯片的互插器實(shí)現(xiàn)芯片間的互連,并通過 RDL 層實(shí)現(xiàn)電源和信 號(hào)傳輸,集成最為靈活。

2)InFO(Integrated Fan-Out)是扇出型晶圓級(jí)系統(tǒng)集成技術(shù),包括 InFO_oS、InFO_PoP 和 InFO_LSI。InFO_oS 與 CoWoS-L 相似,芯片間通過局部硅相連再用 RDL 重布層連接芯片和 PCB 基 板,其具有高密度的 RDL 帶寬,適合 HPC 和 5G 通信領(lǐng)域,多用于小芯片消費(fèi)性產(chǎn)品。 InFO_PoP 是全球首款三維扇出型晶圓級(jí)封裝,是 FOWLP 和 PoP 的結(jié)合體,上層 DRAM 芯片通過 TIV(Through InFO Via)與基板相連,再通過凸塊與下層扇出型晶圓級(jí)封 裝的處理器相連形成 3D 結(jié)構(gòu),與 FC_PoP 相比,InFO_PoP 外形更薄,具有更好的電 氣和熱性能,適用于移動(dòng)設(shè)備、HPC 等領(lǐng)域。InFO_LSI 則是在 InFO_oS 的結(jié)構(gòu)基礎(chǔ)上,在基板內(nèi)嵌入了 LSI 以增加互聯(lián)速度,適 用于 HPC 領(lǐng)域。

3)SoIC(System of Integrated Chips)是超高密度芯片 3D 立體堆疊技術(shù),包含 CoW (Chip on Wafer)和 WoW(Wafer on Wafer)兩種方案,其中 CoW 技術(shù)是晶粒層面的互聯(lián), 即將不同尺寸、功能的芯片進(jìn)行異質(zhì)集合,而 WoW 技術(shù)則是直接用整塊晶圓來進(jìn)行互聯(lián), 通過晶圓堆疊工藝實(shí)現(xiàn)同質(zhì)異構(gòu) 3D 硅的集成。 該技術(shù)將多個(gè)小芯片集成在單個(gè)類似于 SoC 的芯片中,具有比原生 SoC 更好的性能。此 外,不同于傳統(tǒng)的中介層或芯片堆疊的方式,該技術(shù)可以在不使用微凸點(diǎn)的情況下直接將 硅金屬層鍵合到硅芯片上,可實(shí)現(xiàn)更小的體積和更少的功耗,是目前業(yè)內(nèi)最先進(jìn)的堆疊互 連技術(shù)之一。 SoIC 屬于前道 3D 制造環(huán)節(jié),而 CoWoS 和 InFO 屬于后道環(huán)節(jié),因此,通過 SoIC 技術(shù)將芯 片集成到類似于 SoC 芯片中,再整合到 CoWoS 或 InFO 工藝中,可以實(shí)現(xiàn)更小的鍵合間隔 和更高的封裝密度。

3.2、英特爾

和臺(tái)積電相似,英特爾也在先進(jìn)封裝領(lǐng)域布局多年,相繼推出 EMIB、Foveros 和 Co-EMIB 等先進(jìn)封裝技術(shù),其 EMIB 技術(shù)和 Foveros 技術(shù)分別對(duì)標(biāo)臺(tái)積電的 CoWoS 技術(shù)和 InFO 技 術(shù),但相關(guān)產(chǎn)品的量產(chǎn)時(shí)間均落后于臺(tái)積電。

1)EMIB(Embedded Multi-Die Interconnect Bridge)是 2.5D 封裝技術(shù),它是在載板中 嵌入硅橋來完成芯片間互聯(lián),而不是采用 2.5D 封裝中常見的硅中介層進(jìn)行互聯(lián)。相比而 言,硅橋接層(Silicon Bridge)面積小、成本低,可以提供更高的帶寬和更低的功耗, 具備設(shè)計(jì)簡單和封裝良率優(yōu)秀等特點(diǎn),但 EMIB 封裝結(jié)構(gòu)并不適用于芯片數(shù)量多且對(duì)于互 聯(lián)性能要求高的產(chǎn)品。

2)Foveros 技術(shù)是英特爾推出的首款 3D 堆疊技術(shù)。Foveros 的頂層芯片以面對(duì)面的方式 (F2F)相連,下方有微凸塊,底層芯片中具有 TSV 硅穿孔,再通過下方的凸塊實(shí)現(xiàn)基板 與上層芯片的連通。與 EMIB 相比,F(xiàn)overos 可以將不同尺寸和用途的芯片整合起來,進(jìn) 行芯片的橫向和縱向的互聯(lián),具有極大的靈活性,適用于小尺寸或者帶寬要求高的產(chǎn)品。

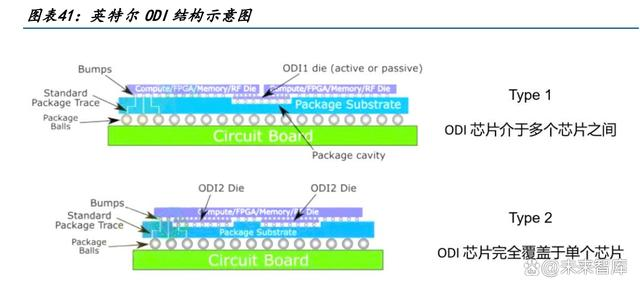

3)Co-EMIB 和 ODI 是英特爾在提升封裝可擴(kuò)展性方面的技術(shù)成果。其中,Co-EMIB 技術(shù)是 EMIB 和 Foveros 的結(jié)合,可以實(shí)現(xiàn)多個(gè) Foveros 結(jié)構(gòu)元件的互連。ODI(Omni Directional Interconnect)技術(shù)主要有兩種類型,Type 1 類似于 EMIB 結(jié)構(gòu),底層芯片居于頂層芯片 之間,芯片間通過 ODI 實(shí)現(xiàn)水平互連,Type 2 類似于 Foveros,底層芯片完全被頂層芯片 覆蓋,上下層芯片通過 TSV 進(jìn)行垂直互連。這兩種類型可以與硅中介層混用,針腳數(shù)量遠(yuǎn) 高于傳統(tǒng)封裝技術(shù),具有更高的帶寬和更低的電阻。

3.3、三星

由于臺(tái)積電 CoWoS 技術(shù)的領(lǐng)先優(yōu)勢,三星近年來錯(cuò)失大陸英偉達(dá)和蘋果等巨頭的芯片代工 訂單,與臺(tái)積電的市占率差距不斷擴(kuò)大。為扭轉(zhuǎn)公司封裝技術(shù)的落后局勢,三星持續(xù)發(fā)力, 相繼推出 I-Cube、H-Cube 和 X-Cube 三大先進(jìn)封裝技術(shù)。

1)I-Cube(Interposer Cube)是 2.5D 封裝技術(shù),以 TSV 和 BEOL 技術(shù)為基礎(chǔ),通過水平 并行的方式集合兩個(gè)以上不同尺寸和功能的芯片。根據(jù)中介層的不同,分 I-Cube S 和 ICube E 兩種,分別對(duì)標(biāo)臺(tái)積電的 CoWoS-S 和 CoWoS-R。 I-Cube S 將一塊邏輯芯片和一組高帶寬存儲(chǔ)墻 HBM 放置在硅中介層上,再運(yùn)用凸點(diǎn) 和 TSV 硅通孔技術(shù)連接芯片和 PCB 載板,具有高算力、高帶寬和低延遲等特點(diǎn)。 I-Cube E 無 TSV 結(jié)構(gòu),是在 RDL 中介層中嵌入硅橋來實(shí)現(xiàn)芯片間的互聯(lián),具有精細(xì) 成像的優(yōu)勢。

2)H-Cube(Hybrid Substrate Cube)是 2.5D 封裝技術(shù),通過硅中介層連接邏輯芯片、 HBM和下層的混合基底。其特點(diǎn)在于,通過整合精細(xì)成像的ABF(Ajinomoto Build-up Film) 基板和高密度互聯(lián)(High Density Interconnection,HDI)基板來實(shí)現(xiàn) 2.5D 封裝中更大 尺寸的封裝,專用于需要高性能和大面積封裝技術(shù)的高性能計(jì)算、人工智能、數(shù)據(jù)中心和 網(wǎng)絡(luò)產(chǎn)品等領(lǐng)域。

3)X-Cube(eXtended Cube)是 3D 封裝技術(shù),計(jì)劃在 2024 年實(shí)現(xiàn)量產(chǎn)。該技術(shù)采用在 Z 軸堆疊邏輯裸片的方法,將芯片垂直堆疊起來,大幅縮短互聯(lián)距離、節(jié)省封裝面積,直接 對(duì)標(biāo)臺(tái)積電的 SoIC 技術(shù)。在芯片互聯(lián)方式上,有微凸塊和銅混合鍵合 HCB(Hybrid Copper Bonding)兩種技術(shù),后者可以提供更高的芯片布局靈活性和更高的堆棧芯片密度,具備 高帶寬和低能耗等優(yōu)勢。

3.4、日月光

日月光作為目前全球最大的封裝測試廠商,于 2022 年推出了 VIPack 先進(jìn)封裝平臺(tái),提供 垂直互聯(lián)整合封裝解決方案。此平臺(tái)利用先進(jìn)的重布線層(RDL)制程、嵌入式整合以及 2.5D/3D 封裝技術(shù)實(shí)現(xiàn)超高密度和性能設(shè)計(jì)的三維異質(zhì)封裝結(jié)構(gòu),主要由六大核心封裝技 術(shù)組成。

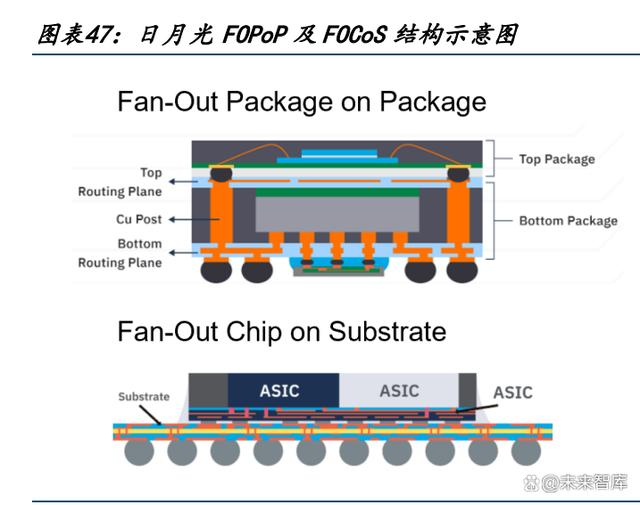

1)FOPoP(Fan-Out Package on Package)是一種基于 RDL 的封裝,它將下層的扇出式封 裝與上層的封裝堆疊在一起,下層封裝的頂部和底部有由銅柱穿模連接的 RDL 重布線層。 與傳統(tǒng) PoP 相比可以進(jìn)一步減小封裝尺寸并提高電氣和熱性能,具有低延遲、小體積和高 帶寬的優(yōu)勢,多用于便攜式電子產(chǎn)品(如智能手機(jī)、平板電腦和可穿戴設(shè)備)等領(lǐng)域。

2)FOCoS(Fan-Out Chip on Substrate)是一種扇出型倒裝封裝,它由兩個(gè) ASIC 芯片組 成,芯片倒扣,通過銅通孔與 RDL 相連(沒有微凸塊),再與具有高引腳數(shù)量的 BGA 基板 封裝。這一技術(shù)可以建立芯片間的短距離連接,以盡可能高效地實(shí)現(xiàn)高密度高效互聯(lián),多 用于高性能計(jì)算領(lǐng)域。

3)FOCoS-Bridge(Fan-Out Chip on Substrate Bridge)是一種 2.5D 封裝,它具有 ASIC 和 HBM 兩個(gè)芯片,兩者通過嵌入 RDL 重布線層的硅橋芯片實(shí)現(xiàn)超細(xì)間距互連。它利用高度 集成的扇出結(jié)構(gòu)的優(yōu)勢,克服了傳統(tǒng)電氣互連的局限性,實(shí)現(xiàn)了處理器、加速器和內(nèi)存模 塊之間高速、低延遲和高能效的數(shù)據(jù)通信,多用于人工智能、高性能計(jì)算應(yīng)用等領(lǐng)域。

4)FOSiP(Fan-Out System in Package)是集合 RDL、載體系統(tǒng)、晶圓級(jí)組裝和屏蔽濺射 幾大技術(shù)的系統(tǒng)級(jí)封裝。其中,扇出型 RDL 提供了優(yōu)于主流基板的精細(xì)線路靈活設(shè)計(jì)能 力,載體系統(tǒng)使薄型晶圓處理成為可能,晶圓級(jí)組裝提供了高速的 SMT 服務(wù),屏蔽濺射技 術(shù)為特定射頻應(yīng)用提供了選擇。FOSiP 具有更高的頻率應(yīng)用、更好的性能和成本效益,廣 泛應(yīng)用于智能手機(jī)、平板電腦、射頻基礎(chǔ)設(shè)施、邊緣計(jì)算和物聯(lián)網(wǎng)等領(lǐng)域。

5)2.5D/3D 封裝是將多個(gè)集成電路封裝在同一封裝內(nèi)的封裝方法。它可以將 GPU、CPU、 HBM 和去耦電容集成在一起,并用帶有 TSV 的硅內(nèi)插層彌合組裝基板和集成電路板之間細(xì) 間距,多用于高端 GPU、5G、人工智能、顯示驅(qū)動(dòng)等領(lǐng)域。

6)CPO(Co-packaged Optics)是將 ASIC 和光引擎共同裝配在同一個(gè)插槽上的共封裝, 其主要是基于硅光電子技術(shù)。硅光子技術(shù)可以利用 CMOS 生態(tài)系統(tǒng)實(shí)現(xiàn)電路高密度光子集 成,并在緊湊型芯片上低成本實(shí)現(xiàn)復(fù)雜的光學(xué)功能。與傳統(tǒng)的集成電路相比,硅光子技術(shù) 具有更高的帶寬和更好的能效,在高速傳輸數(shù)據(jù)時(shí)不會(huì)造成嚴(yán)重的信號(hào)失真,多用于高性 能計(jì)算領(lǐng)域。

3.5、安靠

安靠作為第二大封測龍頭廠商,一直致力于開發(fā)包括硅通孔、穿塑通孔、銅柱、銅混合鍵合等在內(nèi)的技術(shù)工藝,目前主要有 WLCSP、WLFO、WL3D、DSMBGA、AiP/AoP 和 SWIFT/HDFO 六大先進(jìn)封裝技術(shù)。 其中 SWIFT/HDFO 封裝是一項(xiàng)高密度扇出技術(shù)(HDFO),它可以在日益緊湊的封裝結(jié)構(gòu)中通 過 RDL 技術(shù)將多組晶片組裝在一起,彌合了 TSV 和 WLFO 封裝之間的差距。一般來說,SSWIFT 設(shè)計(jì)有 4 層 RDL,第 1 和第 3 層用于信號(hào)路由,第 2 層充當(dāng)接地層,第 4 層則作為 某個(gè)平面或用于銅柱(CuP)互連。

四、投資分析

4.1、封測廠

中國大陸封測廠商在全球化競爭中已占據(jù)重要地位,三家龍頭廠商穩(wěn)居行業(yè)營收前十。根 據(jù)芯思想研究院 2022 年全球委外封測榜單,2022 年全球前三大封測廠商分別為日月光、 安靠和長電科技,市占率合計(jì) 51.9%,行業(yè)集中度較高。在 2022 年?duì)I收前三十榜單中,中 國大陸上榜四家,其中長電科技、通富微電和華天科技穩(wěn)居前十,甬矽電子作為行業(yè)新秀 營收排名達(dá)到二十二名。

長電科技:封測龍頭公司,先進(jìn)封裝打開成長空間

公司是全球第三大,中國大陸第一大半導(dǎo)體封測廠商。公司成立于 1972 年,于 2016 年并 購星科金朋后進(jìn)入發(fā)展快車道。據(jù)芯思想研究院發(fā)布的 2022 年全球委外封測榜單,長電 科技市占率為 10.71%,在全球前十大 OSAT 廠商中排名第三,僅次于臺(tái)灣的日月光和美國 安靠,是中國大陸排名第一的封測企業(yè)。公司擁有三大研發(fā)中心及六大生產(chǎn)基地,本部包 括江陰、滁州、宿遷三大廠,覆蓋傳統(tǒng)高中低端封裝,星科金朋(韓國、新加坡、江陰)、 長電先進(jìn)、長電韓國則以先進(jìn)封裝為主。公司于 2023 年 1 月宣布其 XDFOI Chiplet 高密 度多維異構(gòu)集成系列工藝已按計(jì)劃進(jìn)入穩(wěn)定量產(chǎn)階段,能夠?yàn)閲H客戶提供 4nm 節(jié)點(diǎn)芯片 系統(tǒng)的集成,最大封裝體面積約為 1500mm²。該項(xiàng)技術(shù)可以在高性能計(jì)算、人工智能、5G、 汽車電子等領(lǐng)域應(yīng)用,為客戶提供了外型更輕薄、數(shù)據(jù)傳輸速率更快、功率損耗更小的芯 片成品制造解決方案。

公司產(chǎn)品主要下游應(yīng)用領(lǐng)域包括通信、汽車電子、高性能計(jì)算和存儲(chǔ)等領(lǐng)域。

通信:公司在大顆 FCBGA 封裝測試技術(shù)上已累積十余年經(jīng)驗(yàn),具備從 12x12mm 到 77.5x77.5mm 全尺寸 FCBGA 量產(chǎn)能力。2022 年公司完成 5G 相關(guān)的毫米波 RF 產(chǎn)品和 測試解決方案,WiFi-6e 及 RFFE 模組已投入生產(chǎn)。

汽車電子領(lǐng)域:公司設(shè)有專門的汽車電子事業(yè)中心,產(chǎn)品類型已覆蓋智能座艙、智能 網(wǎng)聯(lián)、ADAS、傳感器和功率器件等多個(gè)應(yīng)用領(lǐng)域。目前海內(nèi)外六大生產(chǎn)基地全部通過 IATF16949 認(rèn)證,并都有車規(guī)產(chǎn)品開發(fā)和量產(chǎn)布局。公司韓國工廠與下游企業(yè)合作研 發(fā)了用于新能源汽車大客戶的芯片,將用于該客戶車載娛樂信息和 ADAS 輔助駕駛。

高性能計(jì)算:公司將研發(fā)投入到高密度多層重布線扇出型封裝技術(shù) FO-MCM,該技術(shù) 可以提供穩(wěn)定高良率的產(chǎn)出。公司產(chǎn)能充足、交期短、質(zhì)量好(良率均能達(dá)到 99.9% 以上),江陰廠區(qū)可滿足客戶從中道封測到系統(tǒng)集成及測試的一站式服務(wù)。

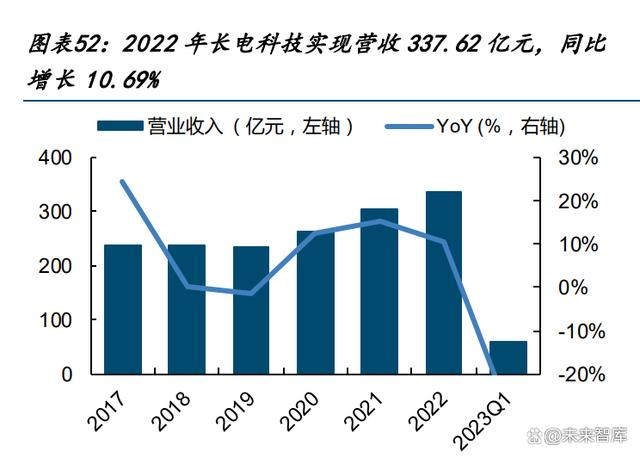

存儲(chǔ):公司服務(wù)覆蓋 DRAM、Flash 等各種存儲(chǔ)芯片,目前已積累 20 多年存儲(chǔ)封裝量 產(chǎn)經(jīng)驗(yàn),16 層 NAND Flash 堆疊、35μm 超薄芯片制程能力、Hybrid 異型堆疊等存儲(chǔ) 封測技術(shù)均處于國內(nèi)行業(yè)領(lǐng)先的地位。 公司 2022 年繼續(xù)保持了營收及利潤的穩(wěn)健增長。公司 2022 年實(shí)現(xiàn)營收 337.62 億元,同 比增長 10.69%;實(shí)現(xiàn)歸母凈利潤 32.31 億元,同比增長 9.20%。展望未來,公司有望受益 于汽車電子、5G 通信、高性能計(jì)算、存儲(chǔ)等高附加值產(chǎn)品結(jié)構(gòu)占比提高。

通富微電:營收增長迅速,先進(jìn)封裝實(shí)力強(qiáng)勁

公司是全球第五大,國內(nèi)第二大封測廠商。據(jù)芯思想研究院發(fā)布的 2022 年全球委外封測 榜單,公司 2022 年?duì)I收規(guī)模首次進(jìn)入全球四強(qiáng)。公司產(chǎn)品種類豐富,廣泛應(yīng)用于高性能 計(jì)算、大數(shù)據(jù)存儲(chǔ)、網(wǎng)絡(luò)通訊、移動(dòng)終端、車載電子、人工智能、物聯(lián)網(wǎng)、工業(yè)智造等領(lǐng) 域。公司共設(shè)有七大生產(chǎn)基地,分別為崇川總部、南通通富、合肥通富、通富超威蘇州、 通富超威檳城、廈門通富和通富通科。公司已覆蓋多個(gè)先進(jìn)封裝工藝,自建 2.5D/3D 產(chǎn)線 全線通線。

公司緊貼 AMD 等龍頭客戶,營收增速高。公司主要客戶有 AMD、恩智浦、聯(lián)發(fā)科、英飛凌、 德州儀器、意法半導(dǎo)體、韋爾股份、兆易創(chuàng)新、卓勝微、艾為電子等。公司目前為 AMD 最 大的封裝測試供應(yīng)商,占其訂單總數(shù)的 80%以上。公司 2022 年度實(shí)現(xiàn)營收 214.29 億元, 同比增長 35.52%;實(shí)現(xiàn)歸母凈利潤 5.02 億元,同比下滑 47.53%。在行業(yè)整體處于下行周 期內(nèi)的階段,公司營收實(shí)現(xiàn)較大幅增長的主要原因大客戶訂單增長較快。但同時(shí),由于受 到匯兌損失和計(jì)提折舊的影響,利潤出現(xiàn)了較大幅度下滑。

華天科技:積極布局先進(jìn)封裝,下行周期業(yè)績承壓

公司是全球第六大,國內(nèi)第三大封測廠商。公司產(chǎn)品主要應(yīng)用于計(jì)算機(jī)、網(wǎng)絡(luò)通訊、消費(fèi) 電子及智能移動(dòng)終端、物聯(lián)網(wǎng)、工業(yè)自動(dòng)化控制、汽車電子等領(lǐng)域。公司目前主要封裝產(chǎn) 品可分為三類: 引線框架類產(chǎn)品:主要包括 DIP/SOP、QFP、QFN、FCQFN、SOT、DFN; 基板類產(chǎn)品:主要包括 WBBGA/LGA、FCCSP/FCLGA、FCBGA、SiP; 晶圓級(jí)產(chǎn)品:定位高端產(chǎn)品,主要包括 WLP 系列、TSV 系列、Bumping 系列和 MEMS 系 列等。

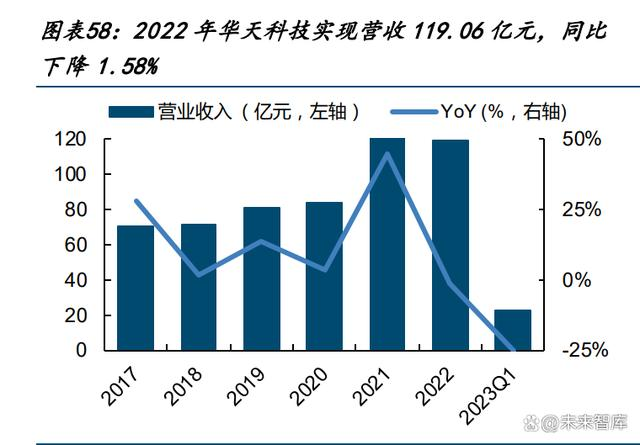

受行業(yè)景氣度下行及終端庫存影響,公司業(yè)績整體承壓。公司 2022 年?duì)I業(yè)收入 119.06 億 元,同比下降 1.58%;歸母凈利潤 7.54 億元,同比下降 46.74%。景氣度低迷的情況延續(xù) 到 23Q1,23Q1 公司實(shí)現(xiàn)營業(yè)收入 22.39 億元,同比下降 25.56%;歸母凈利潤虧損 1.06 億 元,同比下降 151.43%。

甬矽電子:封測行業(yè)新秀,聚焦先進(jìn)封裝

公司是新銳半導(dǎo)體封測廠商,成立之初即聚焦先進(jìn)封裝領(lǐng)域。公司封裝產(chǎn)品主要包括高密 度細(xì)間距凸點(diǎn)倒裝產(chǎn)品(FC 類產(chǎn)品)、系統(tǒng)級(jí)封裝產(chǎn)品(SiP)、扁平無引腳封裝產(chǎn)品 (QFN/DFN)和微機(jī)電系統(tǒng)傳感器(MEMS)四大類別,主要應(yīng)用于射頻前端芯片、AP 類 SoC 芯片、觸控芯片、WiFi 芯片、藍(lán)牙芯片、MCU 等物聯(lián)網(wǎng)芯片、電源管理芯片、計(jì)算類芯片、 工業(yè)類和消費(fèi)類等領(lǐng)域。公司全部產(chǎn)品均為 QFN/DFN、WB-LGA、WB-BGA、Hybrid-BGA、FCLGA 等中高端先進(jìn)封裝形式,在 FC、SIP、QFN/DFN 等先進(jìn)封裝領(lǐng)域具有較為突出的封裝 技術(shù)優(yōu)勢和先進(jìn)性。

受行業(yè)周期下行及低稼動(dòng)率影響,公司利潤大幅下滑。公司 2022 年?duì)I業(yè)收入 21.77 億元, 同比增長 5.96%,歸母凈利潤 1.38 億元,同比下降 57.11%。景氣度低迷的情況延續(xù)到 23Q1, 23Q1 公司實(shí)現(xiàn)營業(yè)收入 4.25 億元,同比下降 26.85%;歸母凈利潤虧損 0.50 億元,同比 下降 170.04%。

公司產(chǎn)品均為中高端先進(jìn)封裝,并且在 SIP、QFN/DFN 等領(lǐng)域具有突出優(yōu)勢。SIP 產(chǎn)品是 公司收入占比最大的業(yè)務(wù),2022 年實(shí)現(xiàn)營收 12.25 億元,營收占比 56.28%,毛利率為 24.1%;QFN 產(chǎn)品 2022 年實(shí)現(xiàn)營收 6.32 億元,占比為 29.02%,毛利率為 12.0%;FC 產(chǎn)品 毛利率水平較高,2022 年實(shí)現(xiàn)營收 2.92 億元,占比為 13.42%,毛利率達(dá) 31.5%。

晶方科技:大陸晶圓級(jí)封測龍頭

公司布局晶圓級(jí)封測,公司具備 8 英寸和 12 英寸晶圓級(jí)芯片尺寸封裝(WLCSP)技術(shù)的規(guī) 模量產(chǎn)能力,下游產(chǎn)品主要包括 CIS 芯片、TOF 芯片、生物身份識(shí)別芯片、MEMS 芯片等, 廣泛應(yīng)用在手機(jī)、安防監(jiān)控、身份識(shí)別、汽車電子、3D 傳感等電子領(lǐng)域。目前,公司主要 客戶有豪威、格科微、索尼、晶相光電、思特威等。2022 年受行業(yè)周期下行的影響,公司 主營業(yè)務(wù)影像傳感器市場需求疲軟,公司營收及利潤大幅下滑。公司 2022 年實(shí)現(xiàn)營收 11.06 億元,同比下降 21.62%;實(shí)現(xiàn)歸母凈利潤 2.28 億元,同比下降 60.45%。2023 年 Q1 實(shí)現(xiàn)營收 2.23 億元,同比下降 26.85%;實(shí)現(xiàn)歸母凈 0.29 億元,同比下降 68.92%。

4.2、先進(jìn)封裝設(shè)備

先進(jìn)封裝所需半導(dǎo)體設(shè)備涉及前道設(shè)備(刻蝕機(jī)、光刻機(jī)、PVD/CVD、涂膠顯影設(shè)備、清 洗設(shè)備等)、后道封裝設(shè)備(磨片機(jī)、劃片機(jī)、固晶機(jī)、鍵合機(jī)、塑封設(shè)備等)。

華海清科:國產(chǎn) CMP 設(shè)備龍頭

公司是國產(chǎn) CMP 設(shè)備制造的突破者。2013 年,華海清科由清華大學(xué)和天津市政府合資成 立,并于 2014 年研制出了國內(nèi)首臺(tái) 12 英寸 CMP 設(shè)備。CMP 設(shè)備可實(shí)現(xiàn)晶圓或硅片表面納 米級(jí)的全局平坦化,是先進(jìn)封裝后道工序的關(guān)鍵工藝設(shè)備。公司自成立以來一直專注于 CMP 設(shè)備工藝技術(shù)及配套材料的研發(fā),是目前國內(nèi)少數(shù)能提供 12 英寸 CMP 高端半導(dǎo)體設(shè)備的制造商。

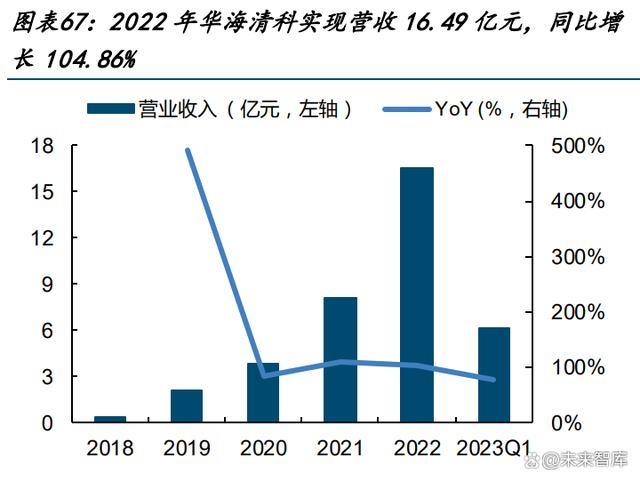

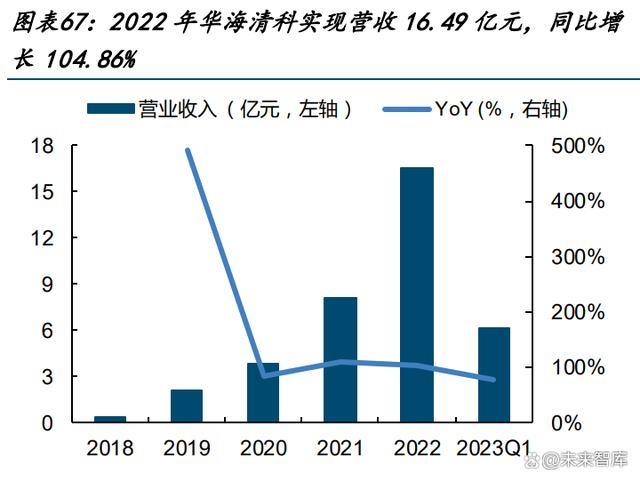

核心產(chǎn)品持續(xù)放量,推動(dòng)營收快速增長。自 2018 年 CMP 產(chǎn)品實(shí)現(xiàn)量產(chǎn)以來,公司營業(yè)收 入持續(xù)增長,2022 年實(shí)現(xiàn)總營收 16.49 億元,2018 年-2022 年?duì)I收 CAGR 達(dá) 160.15%,隨 著經(jīng)營規(guī)模的不斷擴(kuò)張,公司于 2020 年扭虧為盈,2022 年歸母凈利潤達(dá) 5.02 億元,同 比增長 152.98%。作為公司核心產(chǎn)品,CMP 設(shè)備 2022 年?duì)I收 14.31 億元,占總營收 86.77%; 2019 年-2022 年,CMP 設(shè)備業(yè)務(wù)毛利率由 30.16%上升至 47.65%,盈利能力顯著提升。

芯碁微裝:深耕直寫光刻設(shè)備,泛半導(dǎo)體業(yè)務(wù)助力成長

公司是國內(nèi)直寫光刻設(shè)備領(lǐng)軍企業(yè),深耕泛半導(dǎo)體直寫光刻設(shè)備與 PCB 直接曝光設(shè)備領(lǐng) 域。公司一直致力于優(yōu)化 PCB 曝光設(shè)備性能,產(chǎn)品市占率逐步提升。另外公司還積極拓展 業(yè)務(wù)版圖,相繼推出了用于 IC 載板、先進(jìn)封裝、光伏電池曝光等領(lǐng)域的泛半導(dǎo)體直寫光 刻設(shè)備,泛半導(dǎo)體業(yè)務(wù)成為公司的第二成長曲線。 新老業(yè)務(wù)的齊頭并進(jìn),公司收入規(guī)模持續(xù)增長。2022 年公司實(shí)現(xiàn)營收 6.52 億元,2018 年 -2022 年?duì)I收 CAGR 達(dá) 65.46%,2023 年 Q1 實(shí)現(xiàn)營收 1.57 億元,同比增長 50.29%;其中, PCB 業(yè)務(wù)和泛半導(dǎo)體業(yè)務(wù) 2022 年分別實(shí)現(xiàn)營收 5.27 億元和 0.96 億元,占比 80.78%和 14.66%,毛利率分別為 37.90%和 65.08%。2022 年和 2023 年 Q1,公司分別實(shí)現(xiàn)凈利潤 1.37 億元和 0.34 億元,同比增長 28.66%和 70.32%。

芯源微:涂膠顯影機(jī)打破國際壟斷,國內(nèi)市場空間廣闊

公司是國內(nèi)少有的涂膠顯影設(shè)備廠商。根據(jù)中商產(chǎn)業(yè)研究院 2022 年數(shù)據(jù),中國大陸的涂 膠顯影設(shè)備市場被國外廠商高度壟斷,日本東京電子市占率達(dá) 91%,而公司市占率僅為 5%, 大陸其他廠商市占率合計(jì) 4%。公司涂膠顯影業(yè)務(wù)起步較早,技術(shù)處于國內(nèi)領(lǐng)先的地位,主 要產(chǎn)品有光刻工序涂膠顯影設(shè)備(涂膠顯影機(jī)、噴膠機(jī))和單片式濕法設(shè)備(清洗機(jī)、去膠 機(jī)、濕法刻蝕機(jī)),可用于 12 英寸、8 英寸、6 英寸及以下的單晶圓處理。 公司營收保持高速增長,涂膠顯影機(jī)技術(shù)優(yōu)勢明顯。2022 年,公司實(shí)現(xiàn)營收 13.85 億元, 同比增長 67.12%,2018 年-2022 年?duì)I收 CAGR 達(dá) 60.25%;2022 年實(shí)現(xiàn)凈利潤 2.00 億元, 同比增長 158.77%,2018 年-2022 年凈利潤 CAGR 達(dá) 60.69%。作為公司的主營業(yè)務(wù),光刻 工序涂膠顯影設(shè)備營收規(guī)模穩(wěn)步增長,2022 年實(shí)現(xiàn)營收 7.57 億元,毛利率為 34.65%, 2018 年-2022 年?duì)I收 CAGR 為 55.64%,五年?duì)I收貢獻(xiàn)均維持在 50%以上。

新益昌:固晶設(shè)備龍頭,LED 及半導(dǎo)體共同驅(qū)動(dòng)業(yè)績成長

公司是深耕固晶設(shè)備領(lǐng)域,是國內(nèi) LED 固晶機(jī)和電容器老化測試智能制造裝備領(lǐng)域的領(lǐng)先 企業(yè)。公司成立于 2006 年,經(jīng)過多年的技術(shù)研發(fā)和積累,不斷拓展業(yè)務(wù)版圖,相繼推出 半導(dǎo)體固晶機(jī)和 Mini LED 固晶機(jī),成為國際固晶機(jī)領(lǐng)域的龍頭廠商。公司部分智能制造 裝備產(chǎn)品核心零部件已實(shí)現(xiàn)自研自產(chǎn),是國內(nèi)少有的具備核心零部件自研自產(chǎn)能力的智能 制造裝備企業(yè)。公司與海內(nèi)外優(yōu)質(zhì)客戶合作緊密,主要客戶包括晶導(dǎo)微、燦瑞科技、通富 微電、國星光電、三安光電、鴻利智匯、瑞豐光電、雷曼光電、三星、億光電子等。 受行業(yè)周期影響,公司業(yè)績承壓。2022 年,公司實(shí)現(xiàn)營收 11.84 億元,同比下降 1.08%, 實(shí)現(xiàn)凈利潤 2.05 億元,同比下降 11.76%。公司的 LED 固晶機(jī)和電容器設(shè)備為營收主要來 源,產(chǎn)品毛利率水平較高。2022 年,LED 封裝設(shè)備實(shí)現(xiàn)營收 9.09 億元,營收占比達(dá) 76.78%, 毛利率 45.05%,電容器設(shè)備實(shí)現(xiàn)營收 2.24 億元,營收占比 18.92%,毛利率 36.20%。

奧特維:光伏串焊機(jī)領(lǐng)軍者,多維布局半導(dǎo)體封測設(shè)備

公司是光伏組件串焊機(jī)設(shè)備的龍頭廠商。公司 2013 年以串焊機(jī)起步,同時(shí)橫向布局鋰電 設(shè)備和半導(dǎo)體設(shè)備領(lǐng)域。公司產(chǎn)品主要應(yīng)用于光伏行業(yè)、鋰電行業(yè)、半導(dǎo)體行業(yè)封測環(huán)節(jié), 主要包括: 光伏設(shè)備:大尺寸超高速多主柵串焊機(jī)、大尺寸超高速硅片分選機(jī)、激光劃片機(jī)、絲 網(wǎng)印刷線、光注入退火爐、單晶爐等; 鋰電設(shè)備:圓柱電芯外觀檢測、動(dòng)力(儲(chǔ)能)模組 PACK 線等; 半導(dǎo)體封測設(shè)備:鋁線鍵合機(jī)。 公司成長曲線多元,營收及凈利潤持續(xù)高速增長。2022 年及 2023 年 Q1,公司實(shí)現(xiàn)營收 35.40億元和10.39億元,同比增長72.94%和66.27%,2018年-2022年?duì)I收CAGR達(dá)56.77%; 2022 年及 2023 年 Q1,公司實(shí)現(xiàn)歸母凈利潤 7.13 億元和 2.21 億元,同比增長 92.25%和 107.42%。

大族激光:激光設(shè)備龍頭企業(yè),多元化業(yè)務(wù)布局初見成效

公司是全球領(lǐng)先的激光設(shè)備廠商,產(chǎn)品全面覆蓋激光工業(yè)應(yīng)用。公司于 1996 年成立,經(jīng) 過二十余年的技術(shù)積累,具備了從基礎(chǔ)器件、整機(jī)設(shè)備到工藝解決方案的垂直一體化能力, 是全球領(lǐng)先的智能制造裝備整體解決方案提供商。公司業(yè)務(wù)包含信息產(chǎn)業(yè)、新能源、半導(dǎo) 體和通用工業(yè)激光加工四大板塊,主要設(shè)備及產(chǎn)品有: 消費(fèi)電子設(shè)備:主要產(chǎn)品為專用激光打標(biāo)設(shè)備、激光焊接設(shè)備、激光鉆孔設(shè)備、防水 氣密性檢測設(shè)備、CNC 數(shù)控機(jī)床等,用于手機(jī)、筆記本電腦、智能手表等消費(fèi)電子產(chǎn)品的生產(chǎn)加工環(huán)節(jié)。 PCB 設(shè)備:主要產(chǎn)品為鉆孔設(shè)備、激光直接成像設(shè)備、成型設(shè)備以及檢測設(shè)備等,面 向鉆孔、曝光、成型、檢測等 PCB 生產(chǎn)的關(guān)鍵工序。 鋰電設(shè)備:主要產(chǎn)品為勻漿、攪拌、涂布、輥壓、模切、分切、卷繞/疊片、電芯組 裝、烘烤、注液、化成分容等加工設(shè)備及自動(dòng)化生產(chǎn)線,用于鋰電池電芯、模組、PACK 段的生產(chǎn)加工環(huán)節(jié)。 光伏設(shè)備:主要產(chǎn)品在光伏電池及組件環(huán)節(jié),包括 topcon 電池生產(chǎn)主設(shè)備:激光硼 摻雜設(shè)備、PECVD(等離子增 強(qiáng)氣相沉積設(shè)備)、LPCVD(低壓化學(xué)氣相沉積設(shè)備)、 擴(kuò)散爐、氧化爐、退火爐,以及組件段的無損劃片機(jī)、劃焊一體機(jī)等。 半導(dǎo)體設(shè)備:主要產(chǎn)品為激光表切、全切設(shè)備,激光內(nèi)部改質(zhì)切割設(shè)備以及刀輪切割 設(shè)備等前道晶圓切割設(shè)備;焊線設(shè)備、固晶設(shè)備、測試編帶設(shè)備等后道封測設(shè)備以及 晶圓自動(dòng)化傳輸設(shè)備,用于半導(dǎo)體及 LED、顯示面板等泛半導(dǎo)體的生產(chǎn)加工環(huán)節(jié)。 通用元件及行業(yè)普及產(chǎn)品:紫外及超快激光器、高功率光纖激光器、中低功率 CO2 激 光器、脈沖光纖激光器、通用運(yùn)動(dòng)控制系統(tǒng)、振鏡、伺服電機(jī)等工業(yè)激光加工設(shè)備及 自動(dòng)化設(shè)備的關(guān)鍵器件。

受消費(fèi)電子及通用制造行業(yè)需求疲軟影響,公司業(yè)績短期承壓。2022 年及 2023 年 Q1,公 司實(shí)現(xiàn)營收 149.61 億元和 24.25 億元,同比下降 8.40%和 28.55%;歸母凈利潤分別為 12.10 億元和 1.42 億元,同比下降 39.35%和 57.15%。展望 2023 年,隨著消費(fèi)電子及 PCB 設(shè)備下游需求企穩(wěn)及公司產(chǎn)品的迭代更新,業(yè)績或?qū)⑿迯?fù);2023 年公司多款第三代半導(dǎo) 體技術(shù)產(chǎn)品有望放量,半導(dǎo)體設(shè)備業(yè)務(wù)有望迎來新一輪高速增長。

光力科技:雙核心業(yè)務(wù)板塊協(xié)同發(fā)展,持續(xù)完善產(chǎn)品線布局

公司是全球排名前三的半導(dǎo)體切割劃片裝備企業(yè)和國內(nèi)領(lǐng)先的半導(dǎo)體封測設(shè)備及關(guān)鍵零 部件企業(yè)。公司自 2015 年上市以來持續(xù)并購世界優(yōu)質(zhì)半導(dǎo)體設(shè)備及高端零部件企業(yè),迅 速擴(kuò)展半導(dǎo)體封測設(shè)備市場,形成半導(dǎo)體封測裝備業(yè)務(wù)及物聯(lián)網(wǎng)安全生產(chǎn)監(jiān)控裝備兩大核 心業(yè)務(wù)板塊的布局。在現(xiàn)在設(shè)備的基礎(chǔ)上產(chǎn)品不斷迭代升級(jí),相繼推出研磨機(jī)、全自動(dòng)數(shù) 字化智能鉆機(jī)等設(shè)備。目前公司主要產(chǎn)品有: 半導(dǎo)體切割設(shè)備:全自動(dòng)雙軸晶圓切割劃片機(jī)、半自動(dòng)雙軸晶圓切割劃片機(jī)、用于第 三代半導(dǎo)體切割的 6 英寸半自動(dòng)單軸切割劃片機(jī)等; 核心零部件:高性能高精度空氣主軸; 刀片:軟刀、硬刀; 物聯(lián)網(wǎng)安全生產(chǎn)監(jiān)控裝備:基于物聯(lián)網(wǎng)的數(shù)字化智能鉆機(jī)。 公司營業(yè)收入持續(xù)增長,主營業(yè)務(wù)毛利率水平穩(wěn)定。2022 年及 2023 年 Q1,公司分別實(shí)現(xiàn) 營收 6.14 億元和 1.43 億元,同比增長 15.89%和 19.16%;2022 年歸母凈利潤為 0.65 億 元,同比下降 44.56%,23 年 Q1 凈利潤 0.22 億元,同比增長 8.62%。2022 年,公司主營 業(yè)務(wù)半導(dǎo)體封測及安全監(jiān)控分別實(shí)現(xiàn) 3.24 億元和 2.91 億元營收,毛利率分別為 42.13%和 65.71%。

耐科裝備:塑料擠出裝備龍頭,封裝設(shè)備業(yè)務(wù)發(fā)展迅猛

公司是國產(chǎn)塑料擠出裝備的龍頭廠商,封裝設(shè)備領(lǐng)域技術(shù)逐步與國際接軌。公司成立之初 以塑料擠出成型設(shè)備為主營業(yè)務(wù),2014 年切入半導(dǎo)體封裝設(shè)備領(lǐng)域后,相繼開拓了通富 微電、華天科技、長電科技等國內(nèi)頭部封裝企業(yè)客戶,進(jìn)入發(fā)展快車道。公司的主要產(chǎn)品 有: 塑料擠出成型模具和裝置:模頭、定型模、冷卻水箱和定型塊、后共擠裝置; 塑料擠出成型下游設(shè)備:定型臺(tái)、牽引切割機(jī); 半導(dǎo)體封裝模具:切筋成型模具、MGP 模具; 半導(dǎo)體封裝設(shè)備:全自動(dòng)封裝設(shè)備、模塊組合式全自動(dòng)切筋成型設(shè)備、一體式自動(dòng)切 筋成型設(shè)備、塑料封裝壓機(jī)。 半導(dǎo)體業(yè)務(wù)持續(xù)發(fā)力,公司業(yè)績保持高增長。2022 年,公司實(shí)現(xiàn)營收 2.69 億元,同比增 長 8.19%,2018 年-2022 年,營收 CAGR 達(dá) 43.75%;2022 年,公司實(shí)現(xiàn)凈利潤 0.57 億元, 2018 年-2022 年,凈利潤 CAGR 達(dá) 58.64%。自 2019 年公司半導(dǎo)體全自動(dòng)封裝設(shè)備 NTAMS120 和全自動(dòng)切筋成型設(shè)備問世,公司半導(dǎo)體封裝設(shè)備及模具業(yè)務(wù)營收貢獻(xiàn)逐年增長,2022 年 實(shí)現(xiàn)營收 1.63 億元,占比達(dá) 60.58%。

下一頁

下一頁

更多新聞

祝賀公司“面向半導(dǎo)體封測及相關(guān)產(chǎn)業(yè)鏈企業(yè)的工業(yè)互聯(lián)網(wǎng)數(shù)字化車間項(xiàng)目”成功入選“2023深圳數(shù)字化轉(zhuǎn)型優(yōu)秀應(yīng)用成果”

2024-01-31

Copyright ? 2022深圳市盛元半導(dǎo)體有限公司 ALL RIGHT SERVER